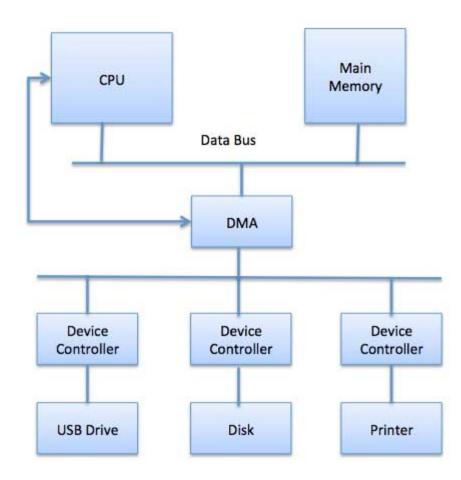

## Direct Memory Access (DMA)

Slow devices like keyboards will generate an interrupt to the main CPU after each byte is transferred. If a fast device such as a disk generated an interrupt for each byte, the operating system would spend most of its time handling these interrupts. So a typical computer uses direct memory access (DMA) hardware to reduce this overhead.

Direct Memory Access (DMA) means CPU grants I/O module authority to read from or write to memory without involvement. DMA module itself controls exchange of data between main memory and the I/O device. CPU is only involved at the beginning and end of the transfer and interrupted only after entire block has been transferred.

Direct Memory Access needs a special hardware called DMA controller (DMAC) that manages the data transfers and arbitrates access to the system bus. The controllers are programmed with source and destination pointers (where to read/write the data), counters to track the number of transferred bytes, and settings, which includes I/O and memory types, interrupts and states for the CPU cycles.

The operating system uses the DMA hardware as follows -

| Step | Description                                                                                                           |

|------|-----------------------------------------------------------------------------------------------------------------------|

| 1    | Device driver is instructed to transfer disk data to a buffer address X.                                              |

| 2    | Device driver then instruct disk controller to transfer data to buffer.                                               |

| 3    | Disk controller starts DMA transfer.                                                                                  |

| 4    | Disk controller sends each byte to DMA controller.                                                                    |

| 5    | DMA controller transfers bytes to buffer, increases the memory address, decreases the counter C until C becomes zero. |

| 6    | When C becomes zero, DMA interrupts CPU to signal transfer completion.                                                |